#### Data recording system

22

0

...

ATT 11

9

21

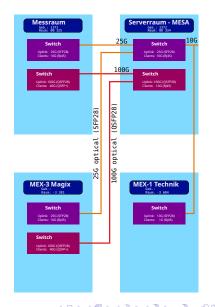

#### Network

- Idea: Two networks with different speeds

- Data network

- Fast connection between switches (up to 100G, optical, higher speed possible)

- 40G connection with SADCs possible

- 10G connection as alternative for SADC connection

- 10G connection to server

- Data connection for BASKET

- Control network

- 25G connection between switches (optical)

- Up to 10G connection to server, PCs, equipment, ...

## Network - Current status

- Plan for the network structure available

- 2 optical fibre cables in place

- Connection: Server room  $\Leftrightarrow$  MAGIX bunker

- Multimode (OM5) with 12 fibres each

- $ightarrow\,$  6 network links per cable possible

- $\bullet~$  No connectors yet  $\rightarrow$  splicing needed

- Control network:

- Should they be POE (power over ethernet) capable?

- Data network:

- Open question: connection for SADC 40/10G?

- Switches, optical fibre cables, ethernet cables, various tranceivers (100G, 40G, 25G, 10G) could be ordered

24.06.2025

3/11

# Computing - Server

- Ubuntu server 24.04 LTS running on all servers

- 6 DB / Event builder

- AMD EPYC 7232P (8 Cores)

- 64 GByte RAM

- 2 TByte SSD, 16 TByte zfs-mirror (RAID-1)

- $2 \times 10 G RJ45$  network connection

- 1 analysis server

- AMD EPYC 7352 (24 cores)

- $\bullet~384\,\mathrm{GByte}$  RAM

- 2 TByte SSD, 64 TByte zRAID2 (RAID-6)

- $2 \times 10 G RJ45$  network connection

- 1 storage server

- AMD EPYC 7232P (8 Cores)

- $\bullet~192\,{\rm GByte}$  RAM

- 2 TByte SSD, 120 TByte zRAID2 (RAID-6)

- 2x 10G RJ45 network connection

- 2 Uninterruptible Power Supplies installed

- $\bullet~$  Capacity:  $6000\,\mathrm{W}$

- 1G RJ45 network connection

- $\Rightarrow$  Total disk space (with out SSD): 280 TByte

- $\Rightarrow$  Total number of CPU cores: 80 (160 Threads)

# Computing - Control room

- 5 Intel NUC with two displays each available

- Intel Core i5-1340P (4P + 8E cores)

- $\bullet~16\,\mathrm{GByte}$  RAM

- $\bullet~0.5\,\mathrm{TByte}~\mathsf{SSD}$

- 2.5G RJ45 network connection

- Runing Ubuntu 24.04 LTS

- Common user account distributed via LDAP (Lightweight Directory Access Protocol)

#### Data storage

- $\bullet~\mbox{For 11.000}\,h$  hydrogen data

- $\bullet~{\rm Estimated} \sim 1\,{\rm PByte}$  of disk space needed

- Including: SADC (Quartz, Lumi, Halo, Beam monitoring, Polarisation), QDC, Asymmetries

- $\bullet\,$  Long term storage for  $\sim 2\,{\rm PByte}$  needed

- Buy storage from ZDV

- Contract for 5 years, renewal needed afterwards

- Storage on disk and tape

- Alternative: Use own storage server

- Tape storage could be realised together with KPH IT

- 2/3 server with large raid systems (Master, Backup, (HIMSTER))

- $\bullet~$  HIMSTER II has 60  $\times$  10  $\rm TByte$  disks per tray

- PRIMA is already using a large RAID system

- Trays/Storage server from HIMSTER II might be available after upgrade

• MESA will use EPICS for distributing/collecting information from the accelerator

- $\Rightarrow\,$  EPICS based slow control needed

- Hardware with EPICS support (e.g. CAEN HV)

- $\rightarrow~$  Easy to be implemented

- Hardware without EPICS support (e.g. solenoid)

- $\rightarrow\,$  Input Output Controller needs to be developed

- Control system for P2 needs to be developed

- Web based frontend

- DOCKER Container for each controler (Ravis Master thesis)

- PRIMA has developed similar system

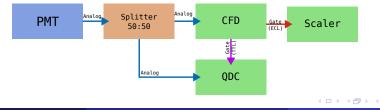

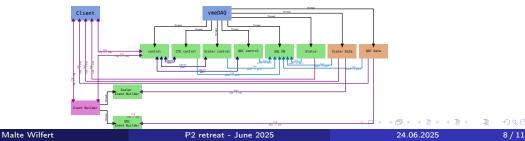

## Tracking mode - readout

- Self triggering system for each quartz bar

- Using new CAEN VME crate

- $\Rightarrow$  Selftriggering successfully tested during test beam August 2024

- $\Rightarrow$  First test of new readout of QDC/CFD/Scaler

- Current Status:

- VME Server

- Split into different processes (Communication, QDC, Scaler, CFD, SQL, Status)

- Currently tested with PMT like pulses from function generator (self triggering)

- Event builder

- Listen/Record to data from server process

- $\bullet~$  Separated for Scaler and QDC

- Possibility to provide trigger signals for each quartz bar via ECL signal

8/11

# Tracking mode - readout

- Self triggering system for each quartz bar

- Using new CAEN VME crate

- $\Rightarrow$  Selftriggering successfully tested during test beam August 2024

- $\Rightarrow$  First test of new readout of QDC/CFD/Scaler

- Current Status:

- VME Server

- Split into diffferent processes (Communication, QDC, Scaler, CFD, SQL, Status)

- Currently tested with PMT like pulses from function generator (self triggering)

- Event builder

- Listen/Record to data from server process

- Separated for Scaler and QDC

- Possibility to provide trigger signals for each quartz bar via ECL signal

#### Integration mode - readout

- Data structure:

- For each helicity window:  $t, \mu, \sigma, \sigma^2, N_{Samples}, \min, \max$

- Same values also for 4 sub windows

- Decission for storage format (ROOT, HDF5, TXT,...)

- TI-boards

- 3 Boards available  $\Rightarrow$  up to 16 Connections

- Synchronisation, run start, individual delays for each connection

- $\bullet\,$  Require at least a  ${\cal T}_{\rm stable}$  signal from source

- All 10 SADC boards and FPGA modules delivered

- Firmware developement for SADC ongoing

- Two different versions for TI-board communication and optical data transfer

- Testing of optical fibre connection ongoing (currently only 1G)

- Calculation of mean values, signal width... not implemented, yet

- Software developement needed

- Development of a Helicity generator (Quadruplets,...)

- Discussion with Anselm and Jürgen

- Anselm developed an FPGA based version of A4 electronics

- Consists of two parts (Master and source front end)

- Developed together with electronics workshop

- $\bullet\,$  Includes De Bruijn Sequence for same amount of  $+ \rightarrow -$  and  $\rightarrow +$  transisions

- We got the schematic from Anseln for these boards

- Develop helicity generator based on this design together with electronics workshop

- Possibility to include TI-firmware on the FPGA for syncronisation with P2-DAQ

- Analysis methodes / Programs for asymmetry calculation need to be developed

- Linear regression algorithms from A4 exists

- $\bullet\,$  Need to be adapted to P2

- Testing of algorithms needed

- Analysis methods for calulation of weak mixing angle need to be developed

- Include possibility for blind analysis

- Provide only calculated asymmetries for each quartz bar instead of measured currents

- Add additinal artificial offset to asymmetry

- Cancels out for linear regression

- $\Rightarrow$  Unblinding by subtracting the offset